Cadence Launches Tensilica Cache-Coherent HiFi 5s SMP for Next-Gen Audio Applications

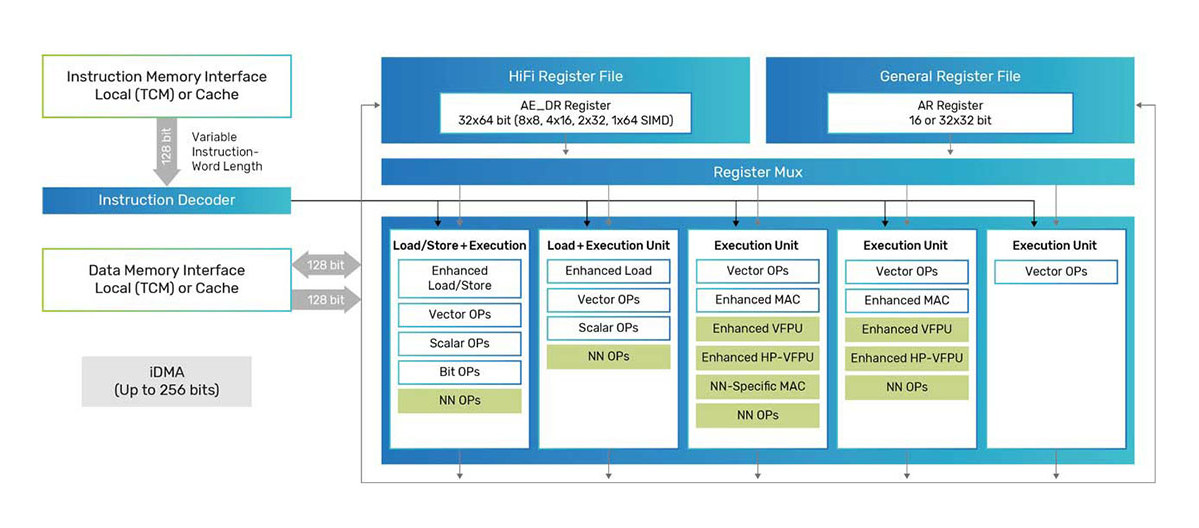

Cadence unveiled a new generation of Cache-Coherent HiFi 5s symmetric multiprocessors (SMP), engineered to drive next-generation audio solutions for challenges such as generative AI-driven sound, immersive experiences, and advanced infotainment systems. The new HiFi 5s multicore DSPs offer scalable performance across 2-8 cores, a streamlined multicore programming with cache coherency, and compatibility with trusted platforms such as Zephyr and FreeRTOS. This accelerates audio development, simplifying considerably software design and optimization.

Next-generation consumer and automotive audio is becoming increasingly sophisticated, and market drivers such as generative AI-based audio processing, immersive soundscapes, and advanced infotainment in software-defined vehicles demand stepped-up audio DSP performance. However, a single DSP can no longer meet escalating compute needs, while multiple DSPs pose significant programming challenges.

Today, OEMs and SoC vendors must perform all multicore hardware design and software development on their own while facing increased time-to-market pressures. At the same time, programmers are grappling with the complexity of software-based synchronization of shared memory regions and the proper partitioning of tasks across the multicore cluster. This can result in designs falling short of performance expectations.

Amid this rapidly evolving landscape, an out-of-the-box hardware design with multicore-enabling operating software is needed to reduce hardware design time and tame the software complexity of multicore audio product development.

To ease the programming of multiple DSPs, Cadence has upgraded its flagship Xtensa LX8 Platform with symmetric multiprocessing capability. The new Xtensa Multicore LX8 Platform allows SoC designers to automatically generate a cluster of up to eight symmetric multiprocessors (SMP) with hardware cache coherency.

Taking its highest-performing and highly successful Tensilica HiFi 5s DSP to even greater heights, Cadence also introduced the first product based on the new platform. The Tensilica Cache-Coherent HiFi 5s SMP delivers scalable performance and higher resource utilization while easing software development for a broad range of audio DSP applications.

Cache-Coherent HiFi 5s SMP

With a design optimized for high-performance, low-power audio applications, the Tensilica Cache-Coherent HiFi 5s SMP scales from two to eight cores and integrates cluster features like interrupt distributor and cross-core debug capabilities. Application development is supported by Zephyr and FreeRTOS, two popular open-source multicore-aware real-time operating systems (RTOS). Multicore support for XOS, Cadence’s RTOS, is planned for later in 2025.

Within a few hours of specifying the HiFi 5s DSP configuration and the number of cores, developers can download the multicore cluster from Cadence’s Xtensa Processor Generator (XPG)—simplifying hardware integration. Designers also receive a complete, multicore-aware Software Development Toolkit (SDK).

The multicore-aware RTOS distributes tasks among the cores and manages cross-core software synchronization, relieving the application of such responsibilities. Cache coherency allows each core of the SMP cluster to have a unified view of memory, thereby avoiding the fragmentation issues and underutilization that often happen with non-coherent multicore designs. This enables the application to easily scale with the number of cores to support different performance requirements.

“From cinemas to homes, phones and now cars, it’s never been easier to enjoy a Dolby Atmos experience,” says Mahesh Balakrishnan, Vice President and General Manager of Consumer Entertainment, Dolby Laboratories. “Our ability to bring innovative audio experiences to consumers is built on a deep collaboration with our partners like Cadence. We are thrilled to celebrate this latest innovation, which will provide OEMs even more options to seamlessly meet the growing demand for next-gen audio.”

“We are excited to see continued innovation with Cadence’s market-leading Tensilica HiFi DSPs. Automotive and TWS Audio applications generated from our highly acclaimed Audio Weaver tool efficiently map to the Tensilica Cache-Coherent HiFi 5s SMP, which offers true concurrent processing for scalable performance. With its hardware cache-coherency, we can avoid the pitfalls of software-based cross-core synchronization, making multicore software development a cinch,” adds Paul Beckman, CTO of DSP Concepts, a long-time Cadence partner. “With AudioWeaver, an OEM can now target significantly higher performance profiles on the Cache-Coherent HiFi 5s SMP in a timely manner and be assured that the utilization of total available memory and cycles for each multicore configuration is being maximized.”

Partner software onboarding is made easy by the unified resource view, which allows sharing of available DSP cycles and total available memory with customers’ code. With hardware managing cache coherency, cross-core related software synchronization bugs are eliminated, resulting in higher product quality and fewer returns. The highly tuned SMP architecture enables audio applications to achieve close to the theoretical maximum performance commensurate with the number of cores. Adaptation to application changes is also greatly facilitated, reducing overall time-to-software completion.

“With growing audio device sophistication comes the challenge of managing complex software and harnessing the full potential of a compute platform with multiple DSPs,” explains Chris Jones, senior group director of product marketing for Tensilica products in the Silicon Solutions Group at Cadence. “Ease of programming and software reliability are increasingly critical for our customers to gain a competitive advantage. Our new, configurable, Tensilica Cache-Coherent HiFi 5s SMP allows customers to efficiently scale their audio products while achieving higher resource utilization and accelerating time to market.”

Leveraging the best-in-class instruction set extensibility of the Xtensa platform, developers can augment the HiFi 5s ISA to optimize their application. The Xtensa SDK includes a SystemC model to facilitate rapid software development. Companies can expeditiously offer the right feature set for each product SKU by choosing from a vast array of HiFi-optimized software packages and audio / voice / speech codecs available from Cadence and its 200+ strong partner ecosystem.

Having already achieved early customer adoption, the Cache-Coherent HiFi 5s SMP is now available. Developers can quickly get up to speed with the provided multicore examples included in the SDK.

www.cadence.com

Source link

-GettyImages-1781827238-Malte-Mueller-(cropped).jpg)